ISSN 1989-9572

DOI:10.47750/jett.2020.12.04.030

# ADDRESS-PREDICATED SRAM ARCHITECTURE: DESIGN AND IMPLEMENTATION STRATEGIES

<sup>1</sup>VUPPULA MANOHAR, <sup>2</sup>KOMANDLA SWAPNA, <sup>3</sup>VEMULA SABITHA, <sup>4</sup>KESHIREDDY ANKHITHA, <sup>5</sup>KOKKU DEEPAK

Journal for Educators, Teachers and Trainers, Vol.12 (4)

https://jett.labosfor.com/

Date of Reception: 28 April 2021 Date of Revision: 27 Aug 2021

Date of Acceptance: 18 September 2021

VUPPULA MANOHAR, KOMANDLA SWAPNA, VEMULA SABITHA, KESHIREDDY ANKHITHA, KOKKU DEEPA (2021). ADDRESS-PREDICATED SRAM ARCHITECTURE: DESIGN AND IMPLEMENTATION STRATEGIES. Journal for Educators, Teachers and Trainers, Vol.12(4).230-234.

Journal for Educators, Teachers and Trainers, Vol. 12(4)

ISSN1989 -9572

https://jett.labosfor.com/

## ADDRESS-PREDICATED SRAM ARCHITECTURE: DESIGN AND IMPLEMENTATION STRATEGIES

<sup>1</sup>VUPPULA MANOHAR ,<sup>2</sup>KOMANDLA SWAPNA,<sup>3</sup>VEMULA SABITHA,<sup>4</sup>KESHIREDDY ANKHITHA, <sup>5</sup>KOKKU DEEPAK

<sup>1</sup>Assistant Professor, <sup>23</sup>Associate Professor, <sup>45</sup>Students Department of ECE Vaagdevi College of Engineering, Warangal, Telangana

ABSTRACT: The address-based SRAM architecture that serves as the foundation for this study allows for error-free and fast memory processing. The main objectives of this project are to improve system performance and reduce delays. Before transferring the data to the SRAM control circuit block, BIST first checks the input. In order to provide accurate information, CRC will identify and correct any errors in the data it receives. The address control unit uses the row and column decoders to decode data addresses. A row decoder and a column decoder with a column format are used to decode the data. Finally, the data from the row and column will be saved in an SRAM array. This data will be subject to read and write activities. This is replicated using Xilinx technology. The simulation's findings demonstrate that an efficient output in terms of area and latency is achieved.

**KEYWORDS:** read bit-line (RBL), SRAM bit cells, amplifier, row and column decoders, CRC (cyclic redundancy check), and SRAM bit cells.

LINTRODUCTION: A system on a chip (SoC)'s total performance and area are greatly influenced by Static Random Access Memory (SRAM), which takes up a substantial amount of the SoC. Because region is a major concern when constructing circuits, memory configuration engineers plan to arrange as many cells per segment as would be sensible to allow sharing of auxiliary hardware [1]. The usefulness of the typical 6T and 8T cells is significantly limited by their incapacity to operate at longer durations. In recent years, scaling has been employed to create the enhanced CMOS device [1]. One of the most important characteristics of modern integrated circuits is their ability to operate at minimal power. Smartphones, portable PCs, and other battery-operated devices are becoming less common. The search for innovative technologies and circuit systems that offer better and longer operating conditions is necessary due to the growing and astounding demand for greater battery life. Furthermore, for non-compact applications, lowering power dispersion is becoming an increasingly important basic issue [1]. Additionally, a fundamental event is essential to fulfil the ongoing execution of complex computer programs. But as technology advances, spilling currents emerge as a key argument in favour of autonomous power distribution. Greater curiosity and widespread desire in longer battery life need the pursuit of novel inventions and circuitry.

This provides longer and better operating conditions. Uses The sub-threshold overflowing currents, however, increase rapidly. Circuits operate less safely and dependably as a result of the increased leakage and lower supply voltage. This proposal proposes an active to characterise digital CMOS circuits with a noisy edge, a worthwhile deferral, and a decreased dynamic and spilt power. In order to employ diverse power reduction strategies, three distinct digital CMOS circuits are investigated and presented [3].

Strong, competent processors are now required due to the growing demand in small battery-operated systems. Stop is typically required for applications such as appropriately calculating active productivity. The batteries in the seinserted frames need to be continuously charged. In the remote sensor systems that are deployed to verify the auditory parameters, the problem gets worse over time [4].

Memory structures are now a separate component of modern VLSI architectures. Semiconductor memory is both an essential component of intricate VLSI architectures and a straightforward memory chip. Regularly

pressing as much memory as is realistically expected in a particular place is the dominant model for streamlining. Memory power problems have been brought on by this trend towards smaller figures. Low limit voltage, ultra-slim gate oxide, and the pattern of scaling of device sizes have all been examined by fluctuation and, therefore, by dependability-related problems.

The emergence of battery-powered devices and low force sensor applications has made SRAM's impact more noticeable. The majority of SRAM plan effort has been focused on increasing yield and promoting voltage calling. High thickness, bit-interleaving, and fast differential detection are made possible by the conventionally implemented six transistor (7T) cell in SRAMs; nevertheless, half-select security, read-upset dependability, and clashing per use and compose measurement are all problems. Previous attempts to resolve these problems have used help-met enhancements, or creative twists of events. The majority of shared SRAM was created using multi-VDD biassing to employ voltage level shifters to achieve low power consumption and minimal latency.

#### II. EXISTINGMETHOD:

Although the productivity of current procedure stores puts a strain on the force utilization, the force utilization of SRAMs is discussed. Finally, the five-transits orbit-cell is presented as an intriguing other choice, albeit in a configuration known as 5T-Portless.Because of its superiority, static arbitrary access memories (SRAM) are most frequently used; a chip may have up to 70% of SRAMs in a transistor count or region. The semiconductor industry is characterized by a push for increased corporate and a steadily shrinking size; as a result, the development of an inventive centre is becoming more difficult and expensive.

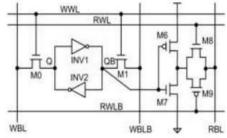

The first SE-10T SRAM cell of the introduced bit cell is appeared in Fig.1.The 6Tcell now has a 4T read port that is built of an inverter and a gearbox door (TG), which restricts the read route from inner capacity hubs. Hub Q Band drives the read bit line (RBL) through TG (M8 and M9), which is constrained by two integral read word lines (WLs). The inverter (M6 and M7) is driven by this. During a read action, this SE-10T cell can totally charge or release RBL by itself. Therefore, setting up a pre charge circuit for RBL is completely unnecessary.

Fig.1: SCHEMATIC OF EXISTING DESIGN

The essential level of unwavering quality becomes difficult to satisfy as memory size increases. For the SRAMs, this causes them to be the faintest in modern innovation hubs.

The for utilization increases as CMOS technology progresses. Low edge voltages are needed for CMOS scaling in conjunction to extremely thin gate oxides to maintain the current drive and keep an eye on limit voltage variations while dealing with short-channel effects. Low limit voltage causes the sub edges pill age current to increase exponentially, which increases the static force utilization. Massive piece lines' capacity can be charged or discharged, which indicates a significant portion of intensity usage during composition or reading jobs. This refers to the dynamic force.

## III. PROPOSEDMETHOD:

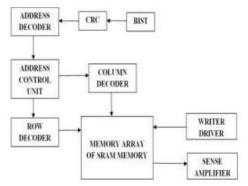

The below figure (2) shows the architecture of proposed system. Initially input is tested unit BIST and transfers the data to SRAM control circuit block. If there are any errors in obtained data CRC will detect and correction and gives the accurate data. Address control unit decodes address of data in two ways they are row decoder and column decoder. Row decoder decodes the data in row format and column decoder will decodes the data in column format. At last the row and column data will be saved in SRAM array memory. From this data will perform read and write operations.

Fig.2: PROPOSED METHOD

#### 1. SRAM

The pressing thickness of integrated circuits (ICs) is constantly increasing and the segment or transistor size is decreasing due to the semiconductor industry's rapid development. Static Random-access memory (SRAM) is a crucial component of modern electronic devices. A base estimated memory cell is enticing for achieving higher coordination thickness of SRAM, but this essentially expands spillage current. Backup spillage is a key component of adding to current spillage in lesser innovation. Because versatile handheld devices like wises can be used in reserve mode for long periods of time, spillage while in this mode is also a real concern because it shortens the battery's life. The circuit is operated at a lower flexible voltage in Complex Metal Oxide Semiconductor (CMOS) technology to reduce leakage current, although doing so slows down the circuit's speed. By using transistors with lower threshold voltages, postponement can be reduced; nevertheless, this boosts the sub-edge spillage current. There are many requirements, and substantial development is necessary to build a memory cell with less backup spilling and greater solidity. Smaller size and lower voltages seriously impair the stability of information in cells. The stability of SRAM depends on the static, which in turn depends on various other cell borders.

## 2. CYCLIC REDUNDANCY CHECK:

The main intent of cyclic redundancy check is to detect the errors and correct the errors.

#### 3. ROWADDRESS

These are the set of cells that generate the word line signals from the word decoders .This structure takes a set of n address lines and generates word lines .At most; one of the word lines is activate time.

**4. COLUMN ADDRESS** Column address select particular bit lines for being connected to sense amplifiers. This is accomplished either by sensing every bit line and getting a few of them out or by using pass gates to enable them to a few sense amplifier inputs

## **RESULTS**

The below figure (3) shows the RTL Schematic of proposed system.

Fig.3: Rtl Schematic Of Proposed System Fig.4: Technology Schematic Of Proposed System The below figure (5) shows the output wave form of proposed system.

Fig.5: Output Wave Form of Proposed System

### **IV.CONCLUSION:**

This led to the design and implementation of an address-based SRAM architecture for fast, error-free memory calculation. The address control unit decodes data addresses in two ways: row decoding and column decoding. This data will be subjected to read and write operations. This is emulated using Xilinx technology. It is evident from the simulation's results that effective.

## **V.REFERENCES:**

- [1] ShouryaGupta,Benton H.Calhoun,"Low-PowerNear-Threshold10TSRAMBit Cells With Enhanced Data-Independent Read Port Leakage for Array Augmentation in 32-nmCMOS",1549- 8328©2018IEEE.

- [2] Chinmay Sharma and Varun Chhabra, "Design of SRAM array using Reversible logic for an efficient SoC design", IEEE, 2017, ISBN 1-5386-1887-5, \$17.00.

- [3] Colin David Karat and Soorya Krishna K, "Design of SRAM Array Using 8T Cell for Low Power Sensor Network", 2015 IEEE, 978-1-4799-9991-0/15/\$31.00

- [4] P.RaikwalDesign and Analysis of Low Power Single Ended 8T SRAM ARRAY (4x4) at 180nm Technology, by V. Neem A. Verma, 978-1-5090-4620-1/16, \$31.00 (2016) IEEE.

- [5] "Design of Low Leakage SRAM Bit-Cell and Array", MSRIT, BANGALORE, India, 21-22 NOVEMBER 2014 by ShashankRanganath, ShankaranarayanaBhat M., and Alden C. Fernandes.